# МОЛОДЕЖНЫЙ НАУЧНО-ТЕХНИЧЕСКИЙ ВЕСТНИК

Издатель ФГБОУ ВПО "МГТУ им. Н.Э. Баумана". Эл No. ФС77-51038.

#### УДК 004

Реализация процессорного модуля 16и разрядного процессора на базе ПЛИС

# 10, сентябрь 2012

Смурыгин И.М.

Научный руководитель: ст. преподаватель Шпиев В.А. МГТУ им. Н.Э.Баумана, Москва, Россия

МГТУ им. Н.Э. Баумана bauman@bmstu.ru

#### Введение

Ядром любой вычислительной системы является вычислительный модуль и его периферийные компоненты, обеспечивающие синхронизацию работы вычислительного ядра и всей системы в целом. Любому инженеру занимающемуся разработкой аппаратуры необходимо знать основы построения процессорных систем и распределения временного пространства.

В работе представлен шинный контролер, обеспечивающий управление временным пространством модуля и контроллер прерываний, отвечающий на прерывания от внешних устройств. Модули реализованы на ПЛИС, т.к. данный метод является наиболее дешевым и позволяет отладить проекты перед запуском в производство на интегральных схемах.

#### Реализация процессорного модуля

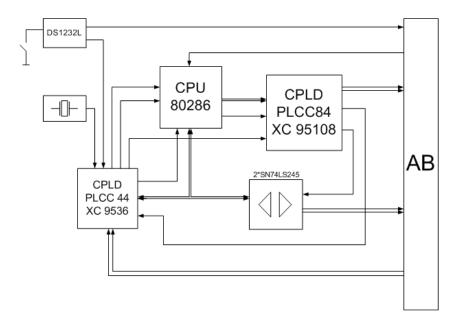

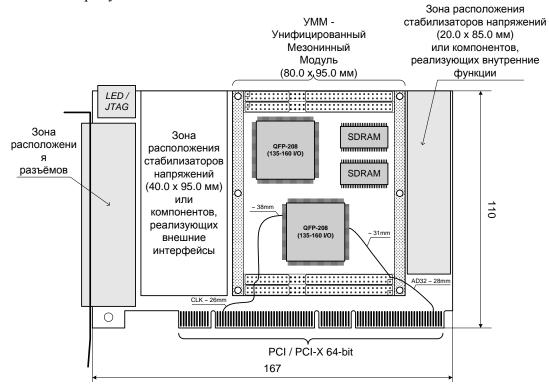

Модуль на 2-х ПЛИС CPLD необходим для реализации временных циклов шины для взаимодействия с асинхронной шиной для передачи различного рода информации. Функциональная схема «мезонина» с интегрированным модулем представлена на рисунке 1.

Основными элементами структурной схемы являются:

- CPU 80286 шестнадцатиразрядный процессор Intel i286;

- кварцевый генератор является источником тактирующего сигнала;

- DS1232L микросхема формирования сигнала сброса;

- 2\*SN74LS245 двунаправленный буфер для хранения и передачи данных;

- **CPLD XC 95108** ПЛИС, внутри которой реализованы шинный контроллер и регистры для хранения текущего адреса выполняемой команды;

- **CPLD XC 9536** ПЛИС, внутри которой реализованы контроллер прерываний и генератор таковых импульсов;

- **AB** (Asynchronous Bus) асинхронная шина.

Рис. 1 – Функциональная схема «мезонина» с интегрированным модулем

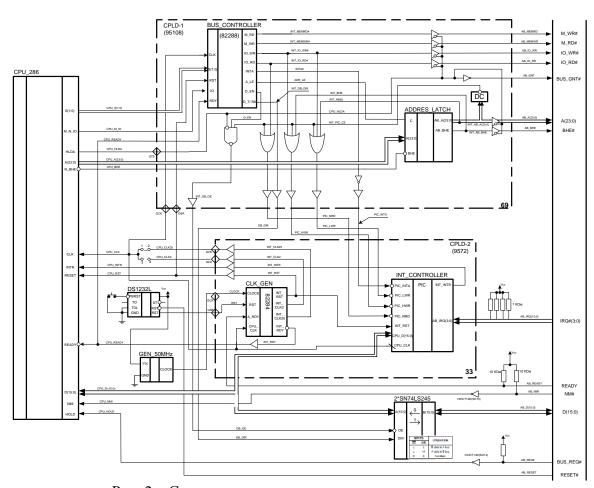

Данная плата проектировалась для специфической задачи обработки данных, поэтому в ней имеются некоторые особенности реализации. Структурная схема модуля «мезонина» представлена на рисунке 2.

Рис. 2 – Структурная схема процессорного модуля

Рассмотрим более подробно основные части данной схемы.

# Шинный контроллер (Bus Controller).

Шинный контроллер предназначен для управления временными циклами шины. Управляется от процессора при помощи следующих сигналов:

- **S1, S0** (Bus cycle status)— сигналы формирующие подциклы в работе цикла шины.

- **COD/<u>INTA</u>**(/Interrupt acknowledge). Определяет циклы работы с устройствами (памятью или внешним устройством), или цикл обработки прерывания ;

- **M/<u>IO</u>** (Memory or Input Output select). Определяет цикл работы с памятью или с внешним устройством. По активному уровню сигнала производиться цикл чтения памяти, а по низкому цикл чтения внешнего устройства.

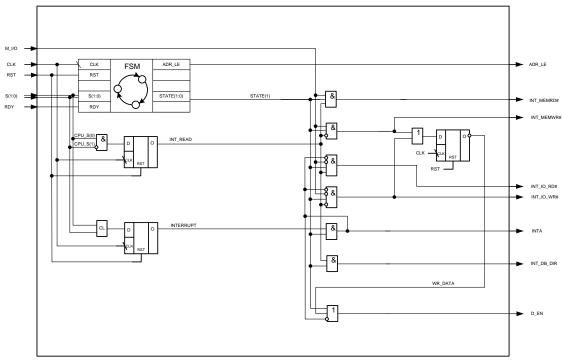

Структурная схема реализации шинного контроллера представлена на рисунке 3. **CPLD XC95108 82288**

Рис. 3 – Структурная схема модуля шинного контроллера

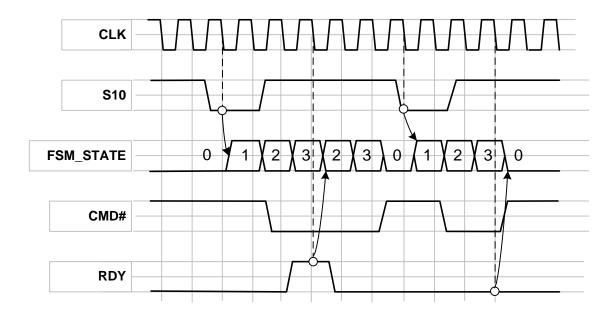

Основную функцию формирования сигналов управления играет схема функционального автомата (FSM). Временная диаграмма его функционирования представлен на рисунке 4.

Спецификация сигналов, отображенных на временной диаграмме, представлена в таблице 1. Таблица 1 — Спецификация сигналов временной диаграммы функционального автомата шинного контроллера

| Сигнал    | Описание сигнала                                                  |  |  |

|-----------|-------------------------------------------------------------------|--|--|

| CLK       | Сигнал тактовой частоты. Синхронизация работы схемы               |  |  |

|           | осуществляется по заднему фронту сигнала                          |  |  |

| S10       | Сигнал, являющийся комбинацией сигналов S1 и S0, получен в        |  |  |

|           | результате их перемножения. Имеет активный уровень логического    |  |  |

|           | нуля                                                              |  |  |

| FSM_STATE | Состояние функционального автомата                                |  |  |

| CMD#      | Command delay. Позволяет задержать начало команды. Имеет активный |  |  |

|           | уровень логического нуля.                                         |  |  |

| RDY       | Сигнал готовности. Сигнализирует о возможности передачи данных по |  |  |

|           | шине.                                                             |  |  |

Рис. 4 – Временная диаграмма работы ступенчатого автомата шинного контроллера

Смысл работы схемы заключается в обработке сигнала RDY. Если процессор сигнализирует о том, что предыдущая операция не закончена (сигнал RDY имеет активный уровень), необходимо вставить дополнительный цикл задержки Т

При помощи сигнала **FSM\_STATE** и простейшей логики формируются сигналы управления шиной и всего модуля, такие как **ADR\_LE**, **MEMRD**, **MEMWR**, **IORD**, **IOWR**, **INTA**, **DB\_DIR**, **D\_EN**.

## Контроллер прерываний (Interrupt controller)

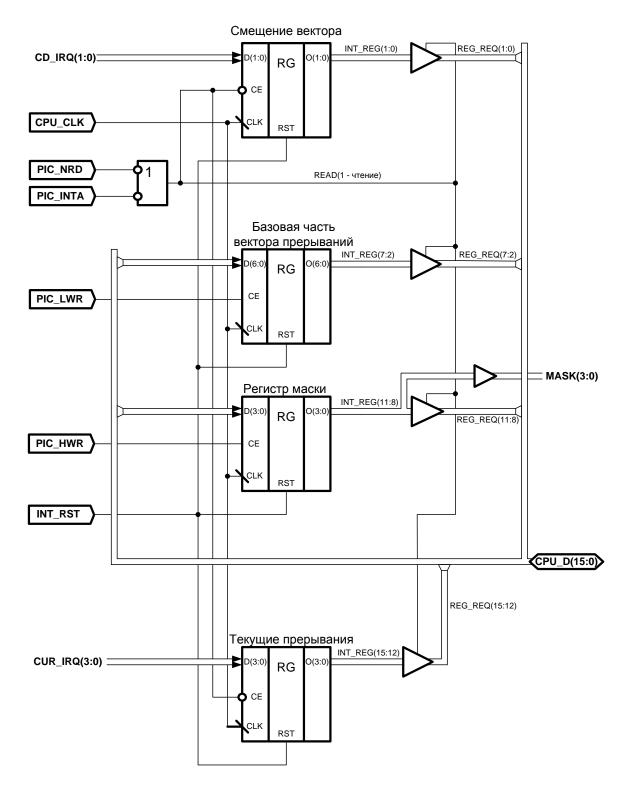

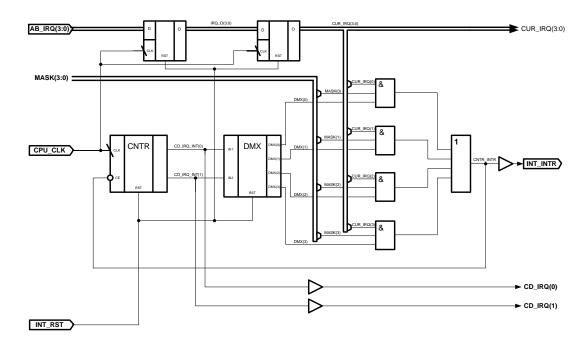

В данной задаче необходимо последовательно обрабатывать 4 обычных прерывания и одно немаскируемое прерывание (NMI-Not Maskeable Interrupt). Для этой цели был разработан контроллер прерываний. Его структурная схема состоит из двух частей. Первая хранит данные о текущем состоянии (рисунок 5), а вторая производит последовательный опрос линий прерываний (рисунок 6).

Тракт данных содержит ряд регистров для хранения информации. Спецификация регистров представлена в таблице 2.

Таблица 2 – Спецификация регистров контроллера прерываний

| Регистр       | Выходной сигнал | Выполняемые функции                                 |

|---------------|-----------------|-----------------------------------------------------|

| Смещение      | INT_REG(1:0)    | Для управления четырьмя векторами прерывания        |

| вектора       |                 | нужно два разряда. Они необходимы для задания       |

|               |                 | смещения относительного главного вектора            |

|               |                 | прерывания при чтении программы из оперативной      |

|               |                 | памяти.                                             |

| Базовая часть | INT_REG(7:2)    | Собственно, вектор прерывания                       |

| вектора       |                 |                                                     |

| прерываний    |                 |                                                     |

| Регистр маски | INT_REG(11:8)   | Есть возможность отключить обработку прерываний     |

|               |                 | при записи маски(8ой разряд отвечает за чтение 0-го |

|               |                 | прерывания, 11ый – Зего прерывания)                 |

| Текущие       | INT_REG(15:12)  | Побитовые значения текущих прерываний               |

| прерывания    |                 |                                                     |

Рис. 5 – Структурная схема тракта данных контроллера прерываний

В результате есть все необходимы значения для чтения определенной инструкции из оперативной памяти. Также имеется возможность работы по отдельным прерываниям при помощи записи маски прерываний.

Рис. 6 - Структурная схема обработки прерываний контроллера прерываний

Данная схема осуществляет последовательный опрос значений прерываний  $AB_IRQ(3:0)$ , поступивших с асинхронной шины, а также отключает обработку прерываний, значения маски которых установлены в 0.

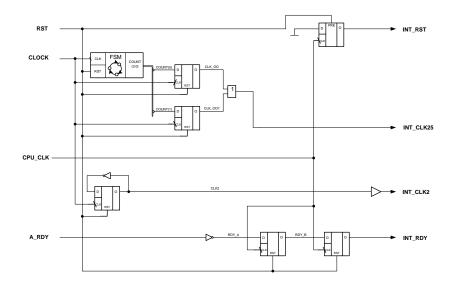

# Тактовый генератор

Предназначен для формирования стабильного сигнала синхронизации с необходимой частотой. Также при помощи тактового генератора формируется сигнал сброса и готовности. Структурная схема тактового генератора представлена на рис. 7

Рис. 7 – Структурная схема тактового генератора

В данном проекте имеется возможность работать с двумя частотами — 12,5 МГц и 10 МГЦ, что достигается путем деления частоты кварцевого генератора на 2 и 2,5. Тактовым генератором генерируется две частоты. Частота, на которой будет работать процессор, выбирается при помощи перемычки на плате. Установление перемычки предусмотрено перед включением устройства.

Данные модули были реализованы на языке VHDL и интегрированы в соответствующие ПЛИС:

- контроллер прерывания и тактовый генератор были интегрированы в ПЛИС **Xilinx CPLD XC 9536**;

- шинный контроллер и буфер ввода вывода адреса были интегрированы в ПЛИС **Xilinx CPLD XC 95108.**

В результате работы был создан модуль для обработки данных и обработки прерываний. Данный модуль предполагается использовать в системах управления и передачи данных. Конструкция макетного устройства предусматривает установку разработанного процессорного модуля на мезонине. Конструкция макетного устройства представлена на рисунке 8.

Рис. 8 – Установка мезонина на основную плату макетируемого устройства

В результате был спроектирован мезонинный модуль, который может быть установлен на плату для обработки различной информации.

# Заключение

Разработка процессорного модуля и распределение временного пространства шины является одной из основных задач при разработке вычислительных систем.

Преимуществом аппаратной реализации проектов на языках HDL на базе ПЛИС является то, что у разработчика есть возможность за небольшую стоимость протестировать определенные варианты решения поставленных задач. Проектирование на ПЛТС обеспечивает легкость реализации различных решений при проектировании.

#### Литература

- 1. Угрюмов Е.П. Цифровая схемотехника: Учеб. Пособие для вузов СПб.: БХВ-Петербург, 2004. 800 с.: ил.

- 2. Б.Брей Микропроцессоры Intel. Архитектура, программирование и интерфейсы. Шестое издание: Пер. с англ. СПб.: БХВ-Петербург, 2005. -1328 с.: ил